# Plasma Etching Rates & Gases Gas ratios affects etch rate & etch ratios to resist/substrate

| Material (M)     | Gas            | Etch Rate<br>(Å/min) | Selectivity |      |                    |

|------------------|----------------|----------------------|-------------|------|--------------------|

|                  |                |                      | M/Resist    | M/Si | M/SiO <sub>2</sub> |

| Si               | $SF_6 + Cl_2$  | 1000-4500            | 5           | _    | 80                 |

| SiO <sub>2</sub> | $CF_4 + H_2$   | 400-500              | 5           | 40   |                    |

| Al, Al-Si, Al-Cu | $BCl_3 + Cl_2$ | 500                  | 5           | 5    | 25                 |

| GaAs             | $CCl_4 + O_2$  | 6000                 |             | _    |                    |

Table 4 Etch Rates and Selectivities for Dry Etching

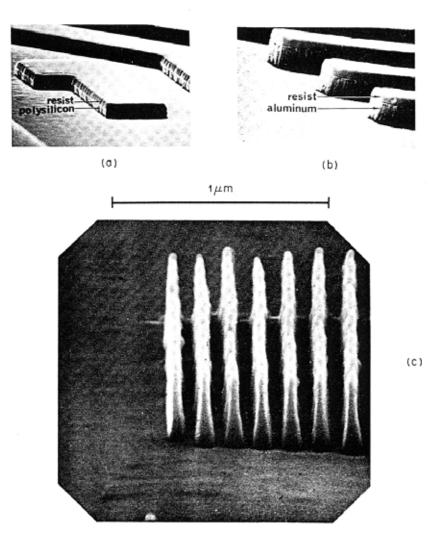

**Fig. 32** SEM micrographs illustrating the results of highly anisotropic etching in reactive plasmas. (a) Plasma-etched pattern in polysilicon film. (b) Plasma-etched pattern in Al-0.7% Cu film. (c) Reactive-ion-etched pattern in a silicon substrate.<sup>3, 28</sup>

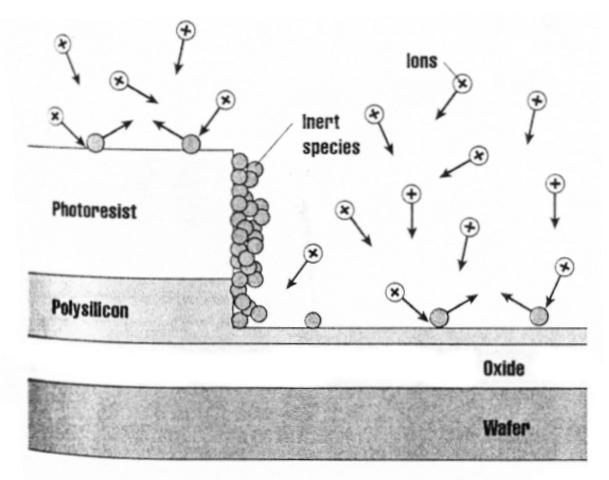

#### **Development of Sidewalls Passivating Films**

- Sidewalls get inert species deposited on them

- Creates passivating (non reacting) layers

- Controls how vertical the sidewalls area

**Figure 11-10** Schematic diagram of a high pressure anisotropic etch showing the formation of sidewall passivating films.

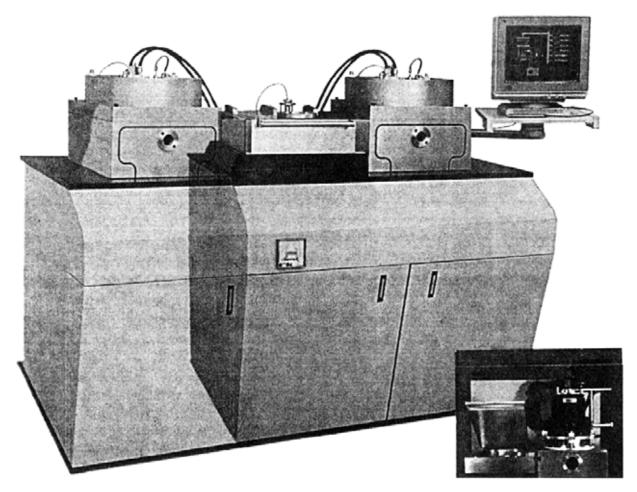

#### **Plasma Etch Station**

- CVD and Plasma Etch stations identical

- Only difference in chemistry used

- Can have same system do both with plate change

- However if use Chlorine chemistry requires stainless steel

- Much more expensive

**Figure 11-13** Photograph of a computer controlled, dual chamber, parallel plate plasma etch system (*courtesy Plasma Therm*).

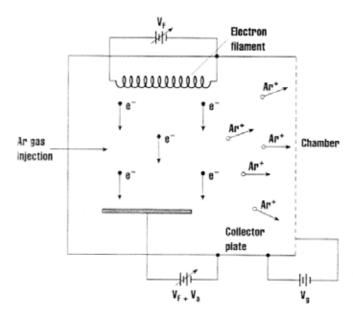

#### **Ion Milling**

- Done at low pressures

- Uses Argon so no reaction

- Simple sputtering type process

- Relatively slow process

- Very Anisotropic

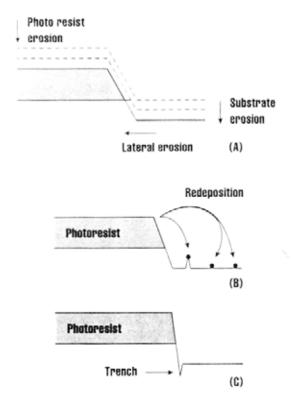

- Problems: Tappered edges, photoresist reposition Trenching

Figure 11-14 Cross section schematic of a Kaufman ion source.

**Figure 11-15** Problems that may occur during ion milling: (a) mask taper transfer, (b) redeposition from the mask, and (c) trenching.

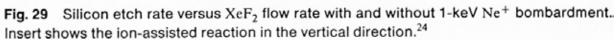

#### **Reactive Ion Etching**

- If increase electrode/substrate voltage get ion bombardment

- Called Reactive Ion etchings

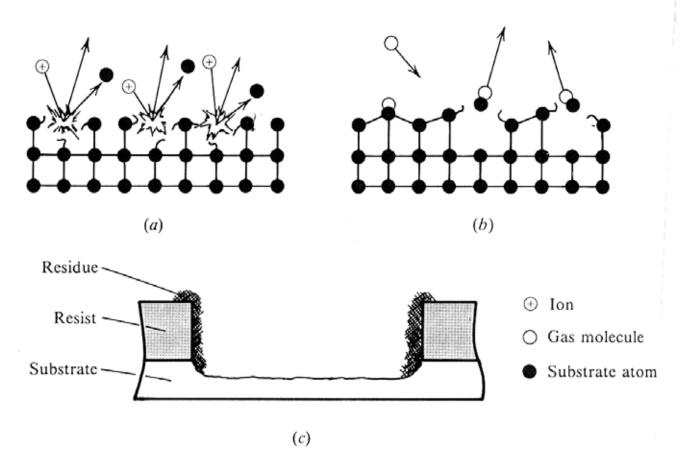

## **Improves Etch Anisotropy in 3 ways**

- Sputtering removal of material

- Heating/bond breaking enhances chemical reactions

- Sputtering removal of protective residues & redeposition on sidewalls

Figure 6-11 Ways in which anisotropic etching is enhanced by ion bombardment in a plasma. (a) Sputtering: physical removal of substrate ions. (b) Heating and bond loosening accelerate chemical reaction with substrate. (c) Sputtering of protective residues in bombarded area enhances reaction rate.

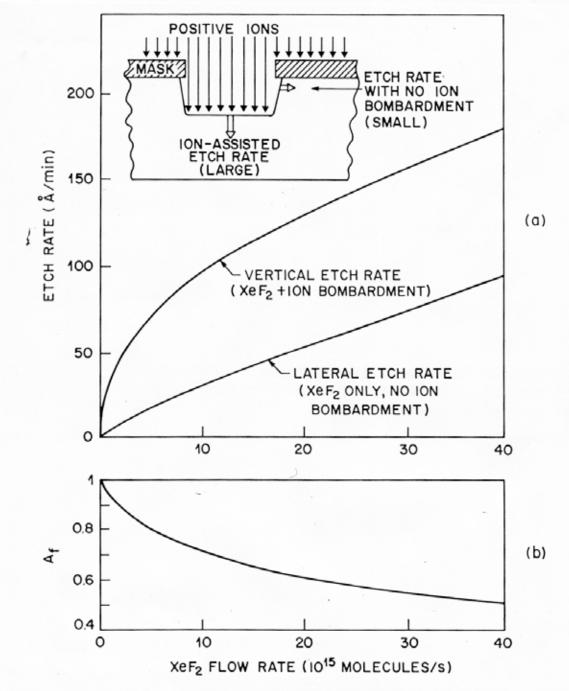

#### Example XeF<sub>2</sub> RIE of Si

- Change in flow rate significantly affects etch rate

- Sideways etching is slower, without ion bombardment

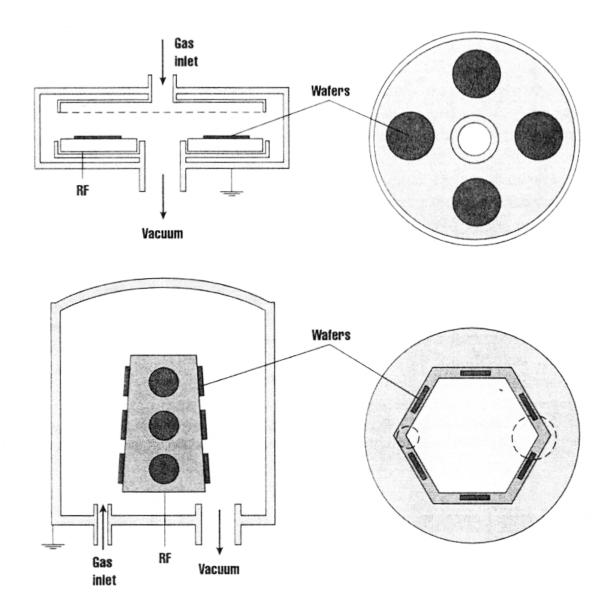

#### **RIE Reactor Types**

- Parallel Plate (1 4 at a time)

- Hexode: does many at time

**Figure 11-17** Top and side views of parallel plate and hexode batch RIE systems. Typical conditions for either is 50 mtorr and 5 kW/m<sup>2</sup>.

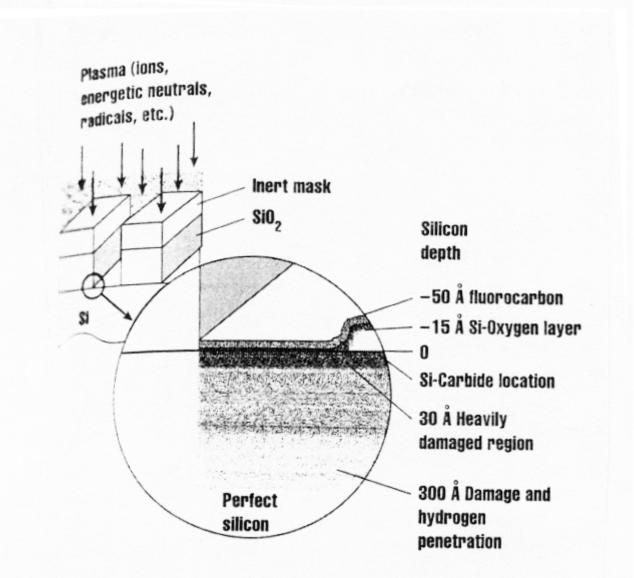

#### **Damaged Surface Due to RIE**

- Deposit many small layers

- Reaction with Photoresists and etch material

- eg When etching oxide down to silicon

- Fluorocarbons, Si-O, Si-Carbide, Si damage & H penetration

- Need to remove damage with Anneals at end.

**Figure 11-20** A cross section schematic of the results of a typical etch of SiO<sub>2</sub> down to Si using  $CF_4/H_2$  (after Oehrlein, Rembetski, and Payne, reprinted by permission, A/P).

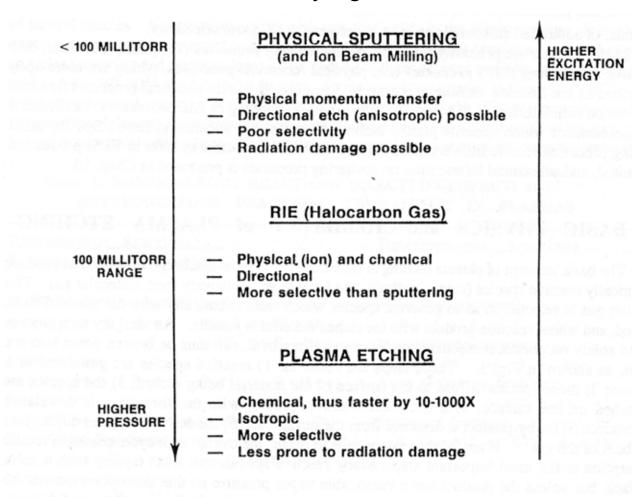

#### **Relationship between Plasma Etching and RIE**

- Pressure higher for Plasma

- RIE excitation and directionality higher

Fig. 2 The dry-etching spectrum.

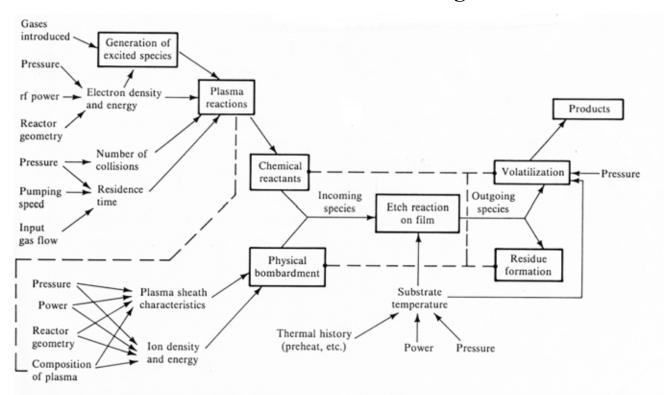

Variables in Plasma Etching/RIE

Figure 6-12 Interaction of variables affecting plasma etching.

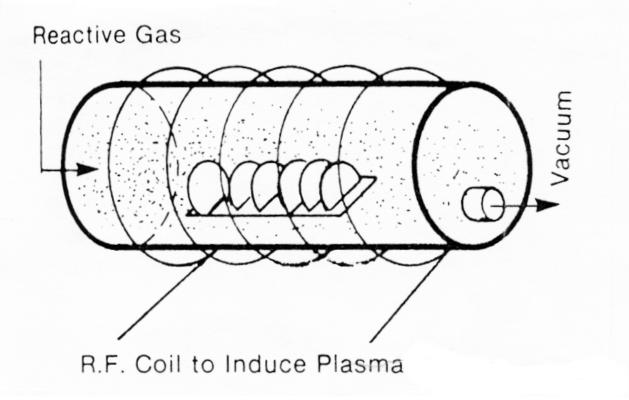

#### **Barrel Reactors**

- Often used for resist stripping with O plasma

- Called Ashing

#### **Post Fabrication Operations**

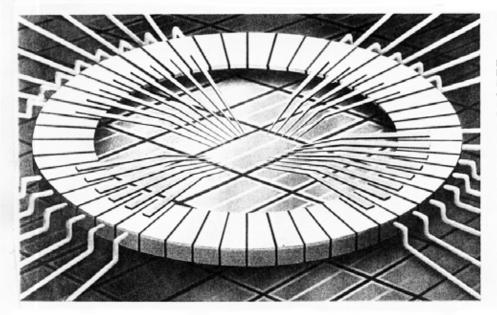

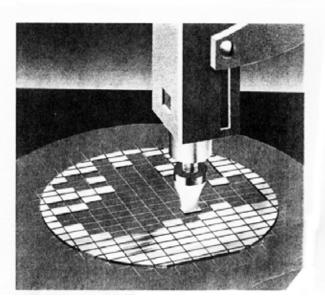

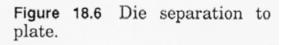

- Die functionally tested •

- Use an automatic prober

- Probe card puts needles on every pad Functional tester tests device

- Difficult to test wafer at full speed

- Bad die marked

- Wafer sawed up & die separated

Probing for flaws. A finished wafer, held on a chuck by suction, is inspected automatically. Probes reach out like tiny fingers from the test instrument that surrounds each chip in turn. Each probe, driven by a computer that feeds signals and records responses, touches a different contact pad on the chip. The rainbow colors are an optical effect created by light refracted by the thin "passivation" layer of silicon dioxide—glass—that coats each chip.

Extracting the good ones. A die picker uses suction to lift only the good chips from the wafer. The machine is guided in its selections by the computer, which uses the wafer map (far left) generated by the testing sequence.

#### **Basic Yield Models**

- Wafers have an average defect  $\lambda$  density/area

- Yield is number of chips that work

- Yield 3% on early runs, 80-90% mature runs

- Wafer production cost does not vary with yield

- Typical production costs

\$1000 per wafer (1 micon 2 metal CMOS)

\$3500 per wafer (0.13 micon 5 metal CMOS)

- But yield determines profit from run

- Initial new complex design may get only 1 chip /wafer

- Often price device at the initial yield

- As yield increase profit increase as production cost fixed

- eg Current Max speed Pentium ~\$1400 yield 1-2 per wafer

After Sort

After Die Separation

#### **Simple Yield modeling**

- Generally assume point defects ie single small defect point

- Map defect distribution at probe time.

- Simple model assumes Poisson Distribution of x defects/die

- Yield of x = 0 defects for chip area S is

$$Y(0,S) = exp(-\lambda S)$$

- Yield is always less than 1

- Note yield drops as chip area increases

- Eg if area S doubles then yield decreases by square

$$Y(0,2S) = exp(-\lambda 2S) = [exp(-\lambda S)]^2 = Y(0,S)^2$$

- eg: Y(0,S) = 0.5, Y(0,2S)=0.25 ie now 75% of wafer fails

- But some chips have more than one defect

- Yield not that simple often

- Process unevenness: Center and edges poor yield

#### **Clustering of Defects**

- Get clustering of defects defects tend to be close together

- Why: simple statisical clusters

- Also what causes one defect causes others

- Studies show this follows a different distribution

- Result is Negative Binomial Distribution probability

$$P(x,S) = \frac{\Gamma(x+\alpha_c)}{x!\Gamma(\alpha_c)} \frac{\left(\frac{\lambda}{\alpha_c}\right)^x}{\left(1+\frac{\lambda}{\alpha_c}\right)^{x+\alpha_c}}$$

Where P = probability of x defects per area S,

$\lambda$  = defect density per chip

$\alpha_c$  = the cluster coefficient.

#### **Clustering of Defects**

- Cluster coefficients start at infinity random Poisson distribution

- $\alpha_c = 1$  is moderate clustering

- $\alpha_c = 0.1$  means most defects near each other

- This gives higher yields for more clustering

- Reason: some chips have many defects

- Leaves more with no defects at given defect density/area

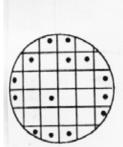

(a)  $\alpha_c = \infty$  (no clustering)

(b)  $\alpha_c=0.1$  (high clustering)

Figure 4.6 Defect Map Example ( $\lambda$ =0.1)

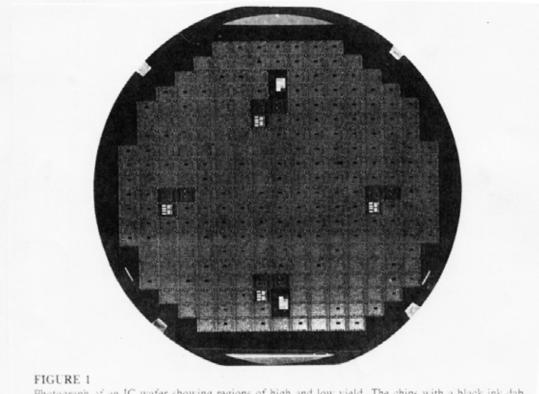

#### **Determining Yield Problems**

- Use chip and test devices

- Use chip electrical test for some defect identification But difficult to isolate that way

- Visual inspection of defect areas also

- Most wafers have test chips on them

- Check yield of test devices: inserted on wafer

- Typical test devices

- sheet resistance all metals, poly, diffusions

- Via and contact chains: checks connections one level to another

- Step coverage devices: conductors over steps

- level to level isolation

- CV diodes to measure threshold

- Transistors characteristics

- Ring Oscillators (chains of odd number of inverters)

Photograph of an IC wafer showing regions of high and low yield. The chips with a black ink dab are bad. The unique-looking chips in the four groups are test chips.

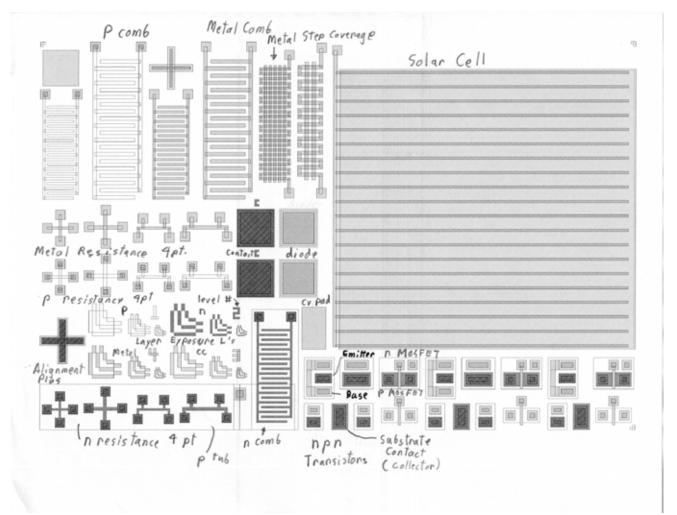

#### **Test Structures on Wafers**

- Wafers have areas of test structures

- Designed to characterize the process

- Lab wafer mostly test structures

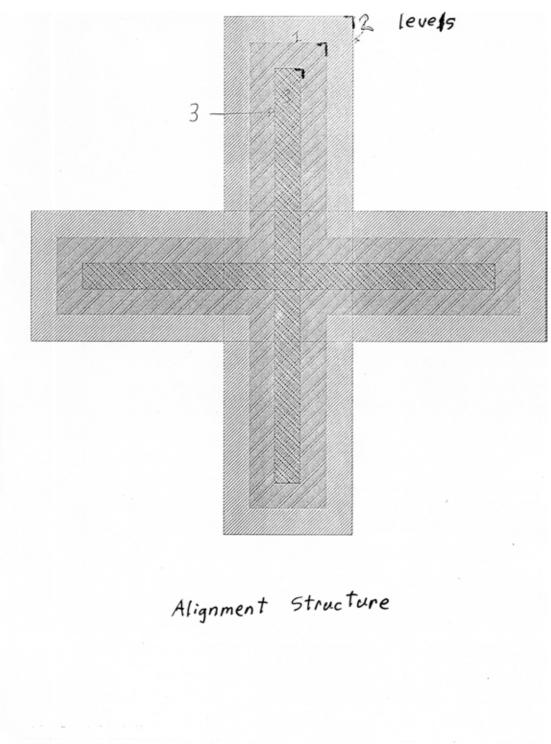

#### **Alignment Cross Structure**

- Note the nesting of light and dark field structures

- Often change alignment structures when reach too may levels otherwise grows to large

- Always align relative to critical level (usually first level)

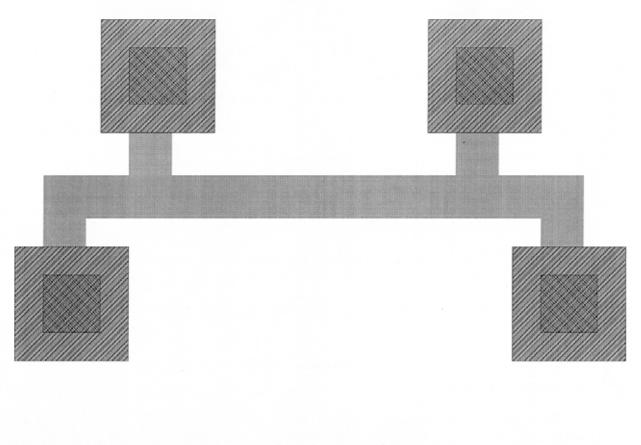

#### **Kalvin 4 Point Probs**

- Used to measure sheet resistance for all layers

- Outer two current, inner two voltage

- Lab ones 7 squares in size

Kelvin sheet resistance

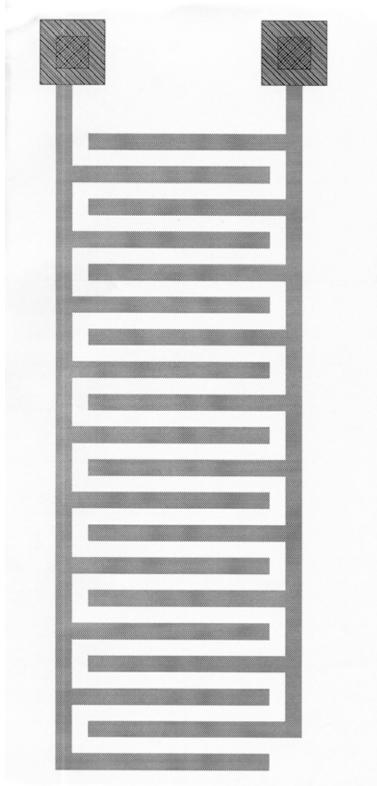

#### **InterDigitated Combs**

• Test for shorts between 2 sides of same level at minimum spacing

Comb short test

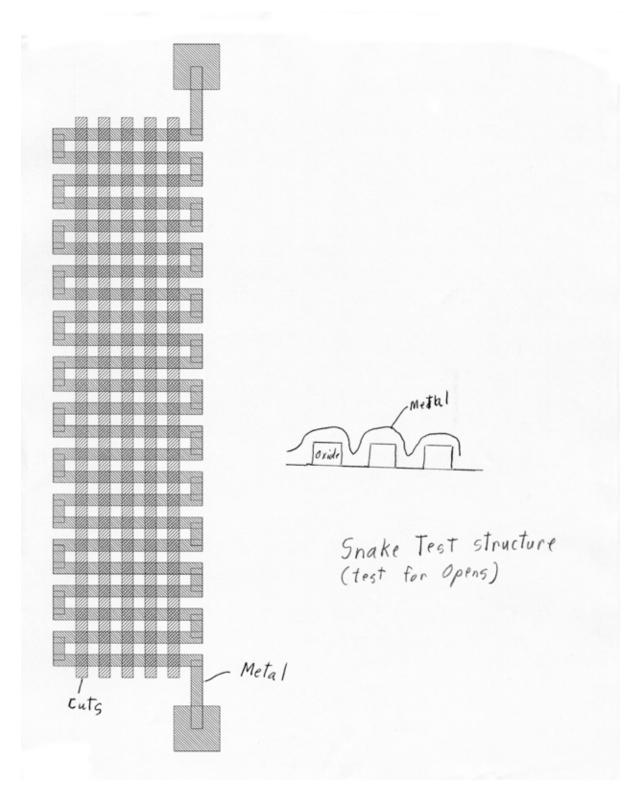

#### Line Snakes over Etched Groves

- Check for breaks as steps over etchs/structures (ie when open)

- Also shorts due to conductor along edges (ie low resistance)

### **Other Common Tests**

- CV measurements of oxide

- Diode characteristics: turn on voltage, reverse current, breakdown voltage, forward resistance

- MOS Transistor Characteristics: Threshold voltage, impedance IV characteristics (transistor curves)

- Bipolar Transistors (if any): IV of BC, BE, EC & Transistor Curves and

- Via and contact cut chairs (via/contact resistance & opens)

- Ring oscillators: feed output of odd number of inverters into input

- Creates oscillator at max transistor speed.

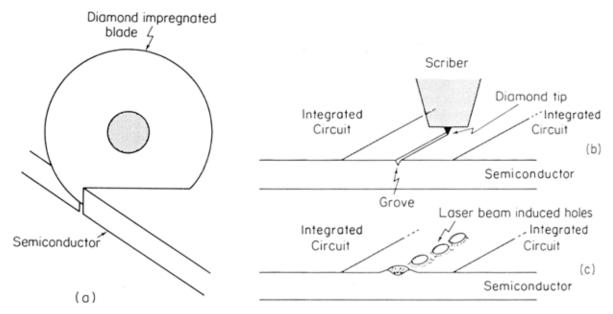

#### Wafer Scribing and Cutting

- Wafer coated to protect die

- Oldest method: diamond tip scribe along d planes bend wafer and snap on planes: loss of die

- Diamond saw cuts in channels problem: chips from cut can damage die

- Laser beam cutting: newest less damage, but more expensive at present

Fig. 6.10 Dicing of ICs: (a) diamond saw; (b) diamond scribe; (c) laser scribing

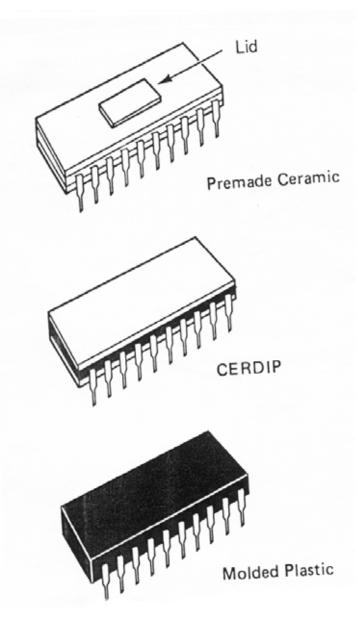

### **Packaging Chips**

- DIP: Dual Inline Pin: up to 64 pins now

- More complex devices mean more complex packages

- Most expensive: Ceramic package with cover used in test samples, small runs

- Sealed ceramic: best for high power

- Molded Plastic: low cost, lower power

Figure 18.17 DIP packages.

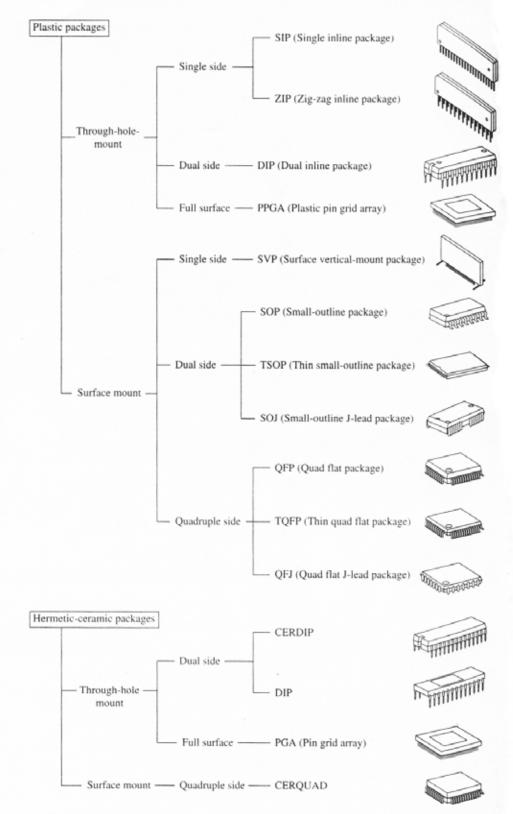

#### More Advanced Packages for lower pin count

#### FIGURE 3

A variety of package designs. Not all ceramic package varieties are shown. (Courtesy of Mirsubisbulletresing Courtes)

#### High Pin Count and Density Packages

- Quad packages: pins on 4 sides

- Pin Grid Arrays (PGA): matrix of pins

- Surface mount: put directly on PC board

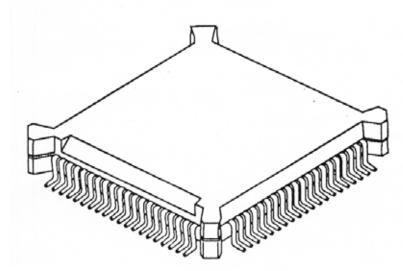

Figure 18.20 Quad package.

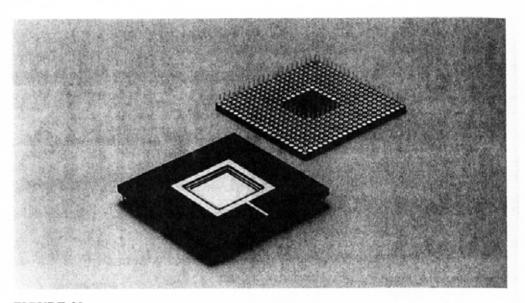

#### **IO and Package**

• Almost all large count packages now Pin Grid Arrays

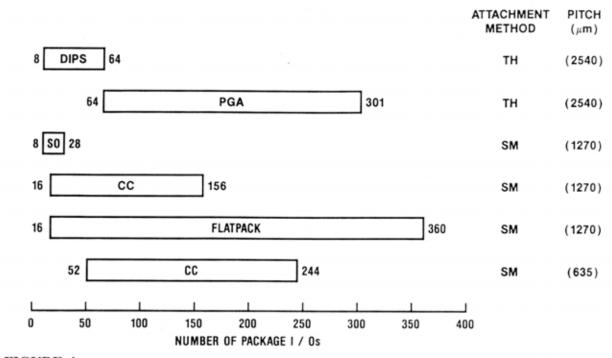

#### FIGURE 4

IC package types as a function of I/Os and method of attachment to PWBs.